# GT-482xx

Preliminary Revision 1.2

1/27/99

# GT-48212 / GT-48208 / GT-48207

Advanced Switched Ethernet Controllers for 10+10/100 BaseX

Please contact Galileo Technology for possible updates before finalizing a design.

# FEATURES

- Single-chip Switched Ethernet Controllers for 10 and 10/100Base-X

- Provides packet switching functions between eight or 12 Ethernet ports and two Auto-Negotiated on-chip Fast Ethernet ports

- Switch expansion via Fast MII port

- Three versions for different cost/performance points

- GT-48212: 12 10BaseT ports, two 100BaseX ports and advanced management features

- GT-48208: eight 10BaseT ports, two 100BaseX ports and advanced management features

- GT-48207: eight 10BaseT ports, two 100BaseX ports with no management features

- Low-cost 32-bit CPU interface for management

- Glueless interface to IDT 3041, Motorola ColdFire, Intel i960®R/Jx CPUs, and GT-641xx controllers.

- Simple interface to other 32/64-bit CPUs

- Management CPU <u>not</u> required

- Allows for cost sensitive unmanaged designs

- Eight or Twelve 802.3 compliant Ethernet ports

- 10Mbps Half-Duplex or 20Mbps Full-Duplex

- Serial mode selectable per port: 10Base-T or FL

- Two Fast Ethernet Media Access Controllers

- Direct Interface to MII

- Half/Full Duplex Support

- IEEE 802.3 100Base-TX, T4, and FX compatible

- Full MII Management Support (MDC/MDIO)

- Auto-Negotiation supported through MII Interface

- Flow Control on all ports

- Standard 802.3x flow control for Full Duplex mode

- Back pressure for Half Duplex mode

- Direct support for packet buffering

- 1Mbyte: using one device 256Kx32-bit Synchronous graphics RAM (SGDRAM)

- 4Mbyte: using two devices 1Mx16bit SDRAM

- Up to 2K buffers, 1536-bytes each, dynamically allocated to the receive queues and CPU

- · High observability LED interface

- Three pin serial LED interface for additional status information per port

- · Advanced address recognition on-chip

- Intelligent address recognition mechanism enables forwarding rate at full wire speed

- Self-learning mechanism

- Supports up to 8K Unicast addresses and unlimited Multicast/Broadcast addresses

- Multicast address support in Address Table

- Broadcast storm filtering

- Extensive network management support

- Repeater MIB counters allowing implementation of four RMON groups

- Hardware assist for Spanning Tree algorithm

- CPU access to Address Table

- CPU Query Ability to read the information from the Address Table

- Ability to define static addresses

- Monitoring (sniffer) mode

- Port locking for security

- Automatic address aging support

- Priority queuing based on MAC address or 802.1Q tag

- Port and MAC address based VLAN

- IP Multicast support

- Flexible software or hardware intervention in packet routing decisions

- Packet sampling management technology

I

- Takes "snapshots" of packets and counters at programmable intervals

- Allows for the implementation of HP-EASE or sampled RMON with low-cost CPUs

- 3.3V with 5V tolerant I/Os

- 208 pin PQFP package

- 12 General Purpose Output pins (LEDs, etc.)

# **Table of Contents**

| 1. | General Description       1         1.1       Fast Ethernet Ports         1.2       Ethernet Ports         1.3       Flow Control and Back Pressure         1.4       CPU Interface         1.5       Synchronous GRAM/DRAM Interface         1.6       Address Recognition         1.7       IP Multicast and VLAN Support         1.8       Priority Queueing         1.9       Network Management Features         1.10       Differences Between the GT-48212, GT-48208 and GT-48207 | 9<br>9<br>0<br>0<br>0<br>1<br>1      |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 2. | Pinout       1         2.1       Pin Functions and Assignment       1                                                                                                                                                                                                                                                                                                                                                                                                                    |                                      |

| 3. | Galaxy Family Overview13.1Basic Operation13.2Address Learning13.3Packet Buffering23.4Packet Forwarding23.5Terminology2                                                                                                                                                                                                                                                                                                                                                                   | 9<br>9<br>0<br>0                     |

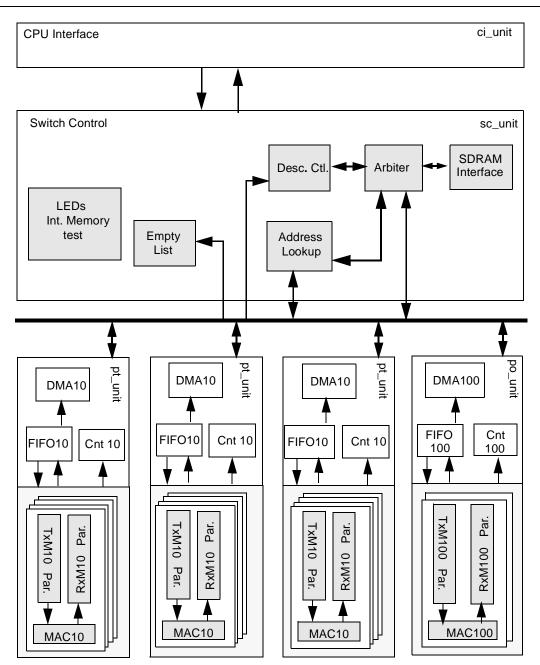

| 4. | Microarchitectural Overview2                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                    |

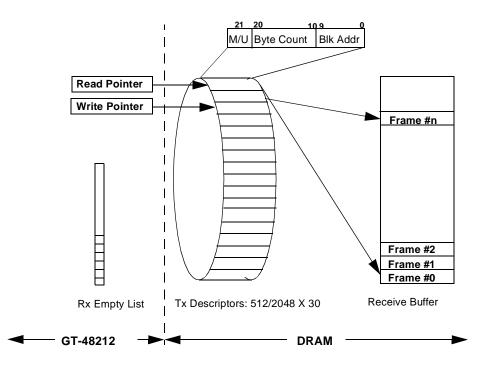

| 5. | Buffers and Queues       2         5.1       Rx Buffer Threshold Programming       2         5.2       Head-of-Line Blocking       2                                                                                                                                                                                                                                                                                                                                                     | 4                                    |

| 6. | MAC Address Table26.1Forwarding Mask26.2Port Number26.3Address Learning Process26.4Locked Port26.5Address Entry Update and Query from CPU26.6Address Recognition26.7Address Aging36.8Static Addresses36.9Address Recognition Failure36.10Forwarding Priority3                                                                                                                                                                                                                            | 6<br>6<br>7<br>7<br>8<br>8<br>0<br>1 |

| 7. | Packet Forwarding       3         7.1       Forwarding a Unicast Packet to a Local Port       3         7.2       Forwarding a Multicast Packet       3         7.3       Forwarding a Packet to the CPU       3         7.4       Forwarding a Packet from the CPU to the GT-482xx       3         7.5       Intervention Mode       3         7.6       IGMP Packet Support       3         7.7       CRC Generation       3         7.8       Tx Watchdog Timer       3               | 3<br>3<br>3<br>4<br>5<br>5<br>5      |

| 8.  | Fast          | Ethernet Interfaces                                      | . 37 |

|-----|---------------|----------------------------------------------------------|------|

|     | 8.1           | 10/100 MII Compatible Interface                          |      |

|     | 8.2           | Media Access Control (MAC)                               |      |

|     | 8.3           | Auto-Negotiation.                                        |      |

|     | 8.4           | Backoff Algorithm Options                                |      |

|     | 8.5<br>8.6    | Data Blinder                                             |      |

|     | 8.7           | 10/100 Mbps MII Transmission                             | .39  |

|     | 8.8           | 10/100 Mbps MII Reception .                              |      |

|     | 8.9           | 10/100 Mbps Full-duplex Operation                        |      |

|     | 8.10          | Illegal Frames                                           |      |

|     | 8.11          | Partition Mode                                           |      |

|     |               | Back Pressure                                            |      |

|     |               | Flow Control                                             |      |

|     | 8.14<br>8.15  | MII Management Interface (SMI)                           |      |

|     | 8.16          | Link Detection and Link Detection Bypass (ForceLinkPass) |      |

|     | 8.17          |                                                          |      |

| •   | <b>E</b> (1), |                                                          |      |

| 9.  |               | rnet (10Mbps) Interfaces                                 |      |

|     | 9.1<br>9.2    | Media Access Control (MAC)                               |      |

|     | 9.2<br>9.3    | Duplex Mode Selection                                    |      |

|     | 9.4           | Backoff Algorithm Options                                |      |

|     | 9.5           | Manchester Encoder/Decoder                               |      |

|     | 9.6           | Link Integrity                                           |      |

|     | 9.7           | Data Blinder                                             |      |

|     | 9.8           | Inter-Packet Gap (IPG).                                  |      |

|     | 9.9<br>9.10   | Partition Mode                                           |      |

|     | 9.10          | Back Pressure                                            |      |

|     |               | Flow Control                                             |      |

|     | -             | Serial Modes                                             | -    |

|     | 9.14          | Physical Interface Circuitry                             | . 47 |

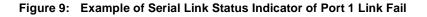

|     | 9.15          | Serial Link Status Indication                            | .47  |

| 10. | Enat          | oling/Disabling Ports                                    | . 48 |

|     |               |                                                          |      |

| 11. | Netw          | /ork Management Support                                  | . 49 |

|     |               | Repeater MIB Counters                                    |      |

|     |               | Spanning Tree (BPDU) Support.                            |      |

|     |               | Broadcast Storm Filtering.                               |      |

| 4.5 |               |                                                          |      |

| 12. |               | et Sampling Technology (HP-EASE)                         |      |

|     |               | Packet Sampling Overview                                 |      |

|     |               | EASE Functionality on the GT-482xx                       |      |

|     |               | EASE Interrupts                                          |      |

|     |               | Sampled Packet Indication                                |      |

|     | 12.6 Error Source Indications      12.7 Enabling/Disabling EASE Functionality                                                                                                                                                                                      |                                        |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 13. | LED Support13.1LED Indications Interface Description13.2Detailed LED Signal Description13.3LED Signal Timing Types13.4LED Interface Description                                                                                                                    | 54<br>54<br>56                         |

| 14. | Interrupts                                                                                                                                                                                                                                                         | 65                                     |

| 15. | <b>RESET Configuration</b> 15.1 Configuration Pins         15.2 Configuration Input Timings                                                                                                                                                                        | 66                                     |

| 16. | CPU Hardware Interface and Address Mapping.16.1Register and Memory Mapping.16.2CPU Interface Modes16.3CPU Interface Pin Definitions16.4Selecting the CPU Mode16.5GT-482xx Base Address16.6CPU Interface Applications16.7CPU Interface Priority16.8Memory Endianess | 69<br>69<br>70<br>70<br>70<br>71<br>79 |

| 17. | SDRAM Interface         17.1       DRAM Configuration         17.2       DRAM Initialization                                                                                                                                                                       | 80                                     |

| 18. | Register Tables18.1Register Description18.2Port MIB Counters (14 Blocks), Offset (start): 0x600, 0xA00, 0xE00, 0x1200                                                                                                                                              | 84                                     |

| 19. | <ul> <li>GT-482xx Pinout Differences</li></ul>                                                                                                                                                                                                                     | 112<br>112<br>112                      |

| 20. | GT-482xx Pinout Tables, 208-PQFP                                                                                                                                                                                                                                   | 114                                    |

| 21. | DC Characteristics - PRELIMINARY/SUBJECT TO CHANGE )                                                                                                                                                                                                               |                                        |

| 22. | AC Timing - TARGET/SUBJECT TO CHANGE                                                                                                                                                                                                                               | 122                                    |

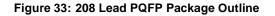

| 23. | Packaging                                                                                                                                                                                                                                                          | 127                                    |

| 24. | Document History                                                                                                                                                                                                                                                   | 129                                    |

| Арр | endix A                                                                                                                                                                                                                                                            | 135                                    |

# List of Figures

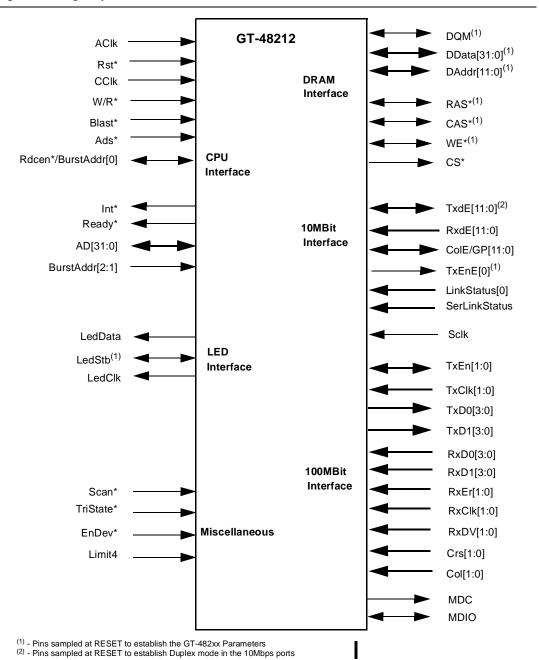

| Figure 1: Logic Symbol                                                  |

|-------------------------------------------------------------------------|

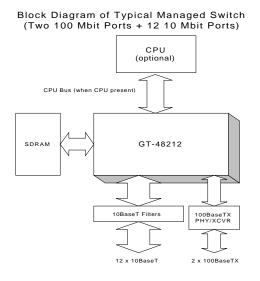

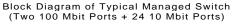

| Figure 2: Block Diagram of the GT-4821222                               |

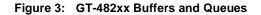

| Figure 3: GT-482xx Buffers and Queues                                   |

| Figure 4: MII Transmit Signal Timing                                    |

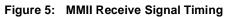

| Figure 5: MMII Receive Signal Timing40                                  |

| Figure 6: MDIO Output Delay43                                           |

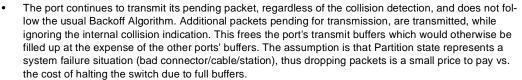

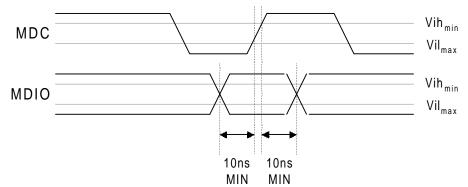

| Figure 7: Required MDIO Setup and Hold Time43                           |

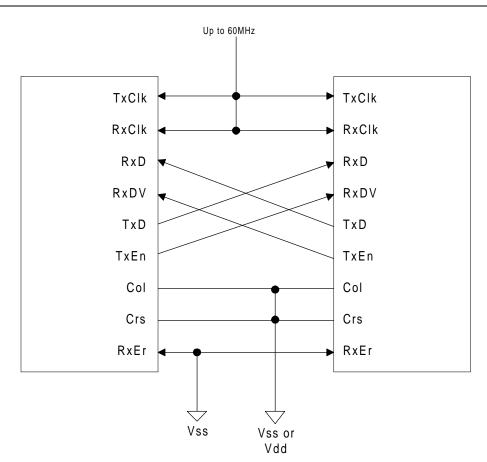

| Figure 8: Expansion MII Wiring Diagram                                  |

| Figure 9: Example of Serial Link Status Indicator of Port 1 Link Fail47 |

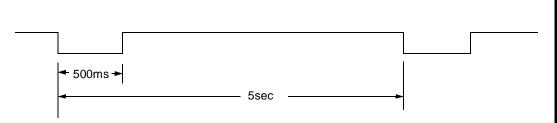

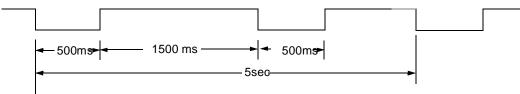

| Figure 10: Primary Status LED Timing (One Blink)55                      |

| Figure 11: Primary Status LED Timing (Two Blinks)55                     |

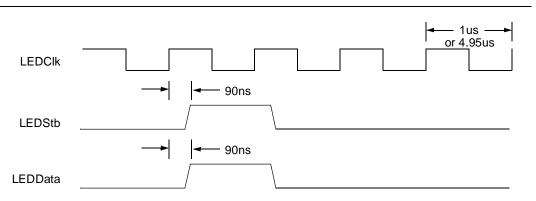

| Figure 12: Serial LED Interface Timings57                               |

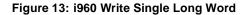

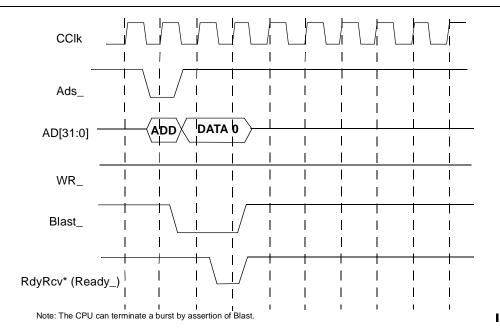

| Figure 13: i960 Write Single Long Word71                                |

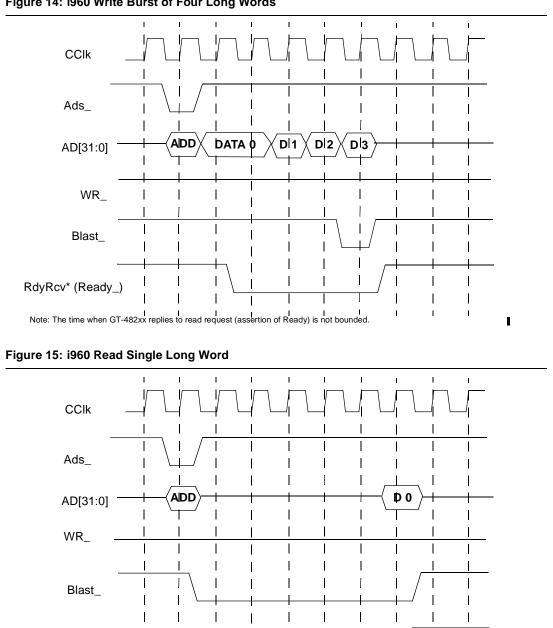

| Figure 14: i960 Write Burst of Four Long Words72                        |

| Figure 15: i960 Read Single Long Word72                                 |

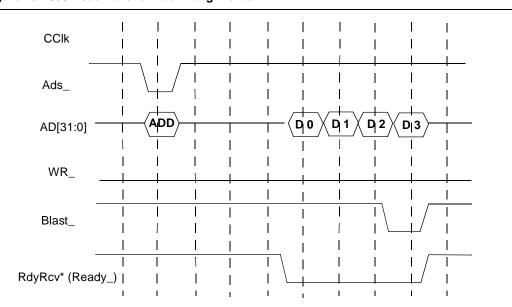

| Figure 16: i960 Read Burst of Four Long Words                           |

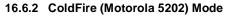

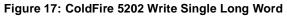

| Figure 17: ColdFire 5202 Write Single Long Word73                       |

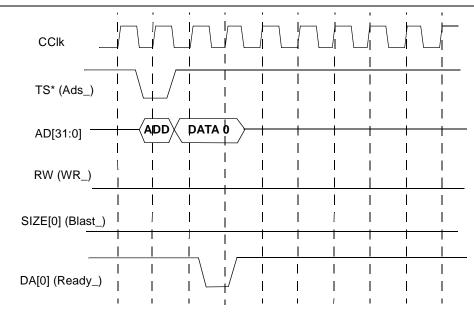

| Figure 18: ColdFire 5202 Write Burst of Four Long Words                 |

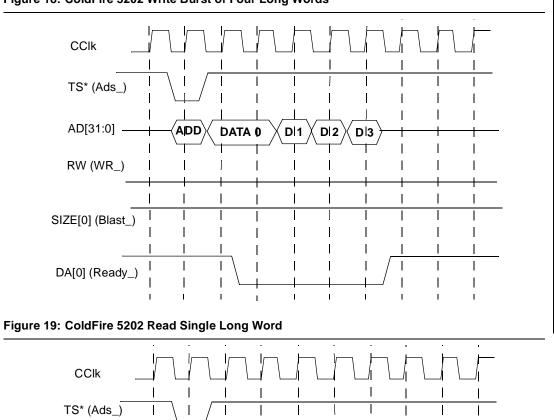

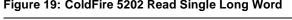

| Figure 19: ColdFire 5202 Read Single Long Word74                        |

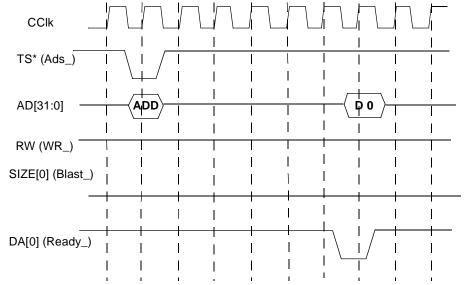

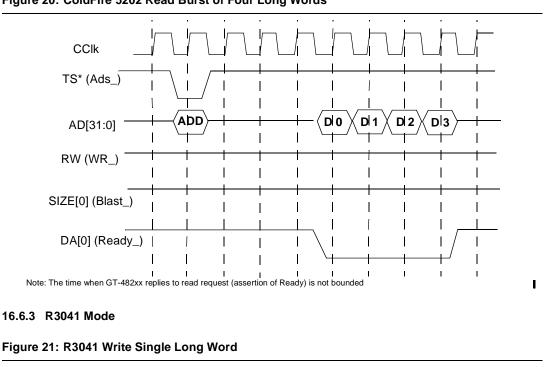

| Figure 20: ColdFire 5202 Read Burst of Four Long Words                  |

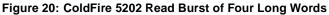

| Figure 21: R3041 Write Single Long Word75                               |

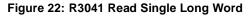

| Figure 22: R3041 Read Single Long Word                                  |

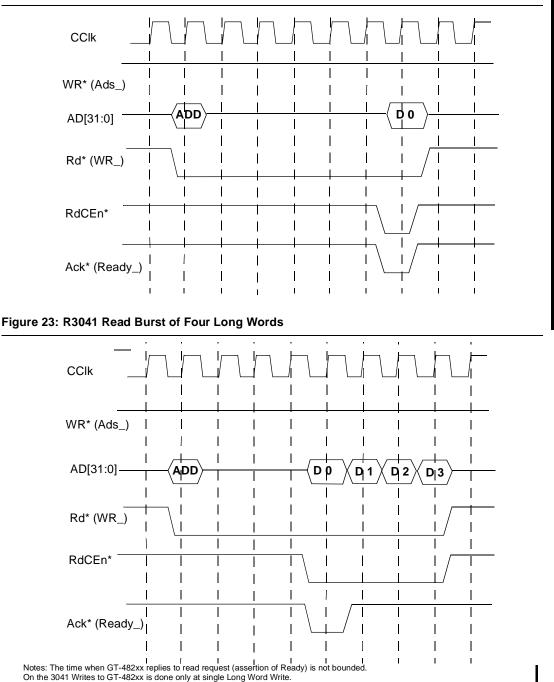

| Figure 23: R3041 Read Burst of Four Long Words                          |

| Figure 24: GT Write Single Long Word                                    |

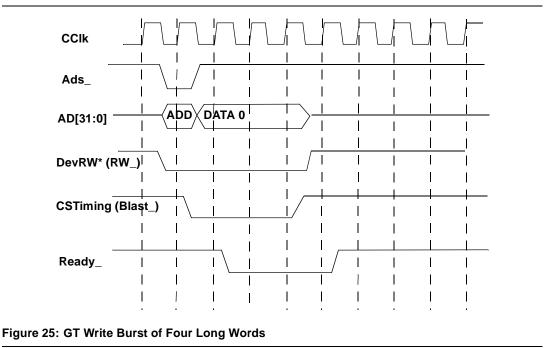

| Figure 25: GT Write Burst of Four Long Words                            |

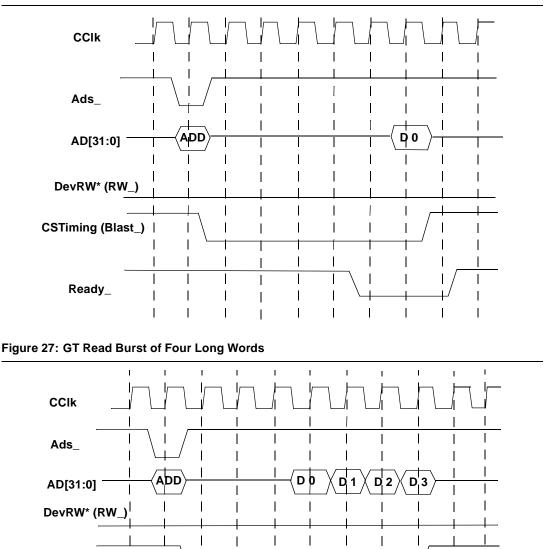

| Figure 26: GT Read Single Long Word                                     |

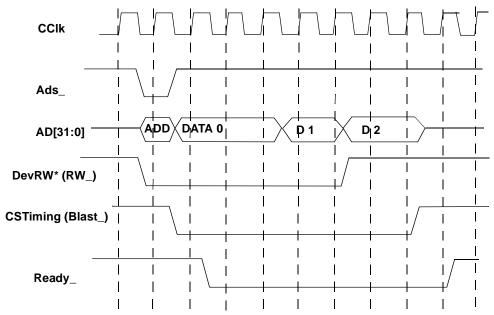

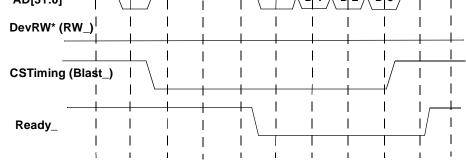

| Figure 27: GT Read Burst of Four Long Words78                           |

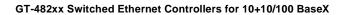

| Figure 28: Serial Clock Waveform (SCIk)                                 |

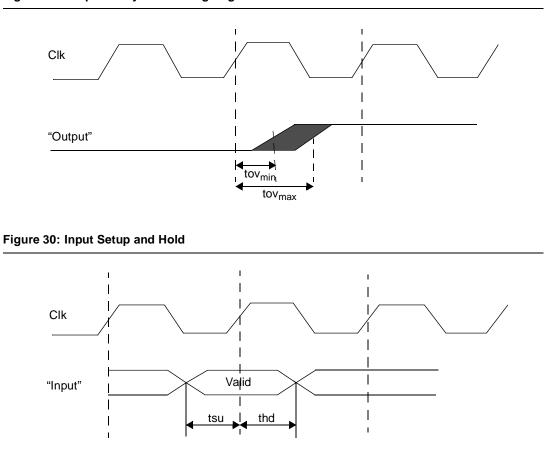

| Figure 29: Output Delay from Rising Edge                                |

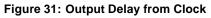

| Figure 30: Input Setup and Hold                                         |

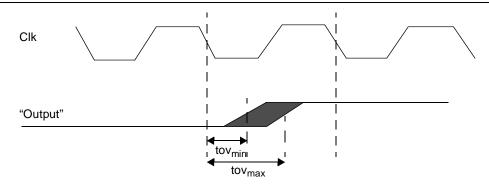

| Figure 31: Output Delay from Clock                                      |

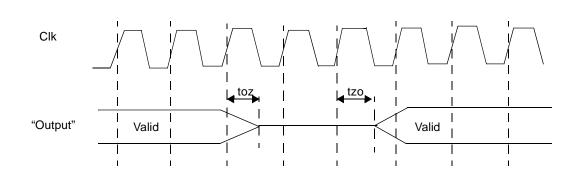

| Figure 32: Output Float and Drive Delay                                 |

| Figure 33: 208 Lead PQFP Package Outline                                |

|                                                                         |

I

# List of Tables

| Table 1 | : Pinout Differences.                  | 12 |

|---------|----------------------------------------|----|

| Table 2 | 2: Pin Functions                       | 14 |

| Table 3 |                                        |    |

| Table 4 |                                        |    |

| Table 5 | ······································ |    |

| Table 6 |                                        |    |

| Table 7 |                                        |    |

| Table 8 |                                        |    |

| Table 9 |                                        |    |

|         | 0: SMI Bit Stream Format               |    |

| Table 1 |                                        |    |

| Table 1 |                                        |    |

| Table 1 |                                        | 54 |

| Table 1 | 0                                      |    |

| Table 1 |                                        |    |

| Table 2 |                                        | 70 |

| Table 2 |                                        |    |

| Table 2 | · · · · · · · · · · · · · · · · · · ·  |    |

| Table 2 |                                        |    |

| Table 2 |                                        |    |

| Table 2 |                                        |    |

| Table 3 |                                        | 92 |

| Table 3 |                                        |    |

| Table 3 | ,                                      |    |

| Table 4 | ,                                      |    |

| Table 4 |                                        |    |

| Table 4 | I7: Rx_10 Threshold, Offset: 0x60      |    |

| Table 48: | Rx_100 Threshold, Offset: 0x64                                                  |

|-----------|---------------------------------------------------------------------------------|

| Table 49: | CPU Threshold, Offset: 0x68100                                                  |

| Table 50: | LED Override, Offset: 0x6C                                                      |

| Table 51: | Flow Control Source Address Low, Offset: 0x70100                                |

| Table 52: | Flow Control Source Address High, Offset: 0x74101                               |

| Table 53: | CPU Time Out Register, Offset: 0x7C                                             |

| Table 54: | DRAM Configuration, Offset: 0x1448101                                           |

| Table 55: | DRAM Parameters, Offset: 0x144C101                                              |

| Table 56: | SDRAM Operation, Offset: 0x1474 102                                             |

| Table 57: | Address Decode, Offset: 0x147C102                                               |

| Table 58: | Port Control (10M ports), Offset: 0x400-0x40C, 0x800 - 0x80C, 0xC00 - 0xC0C 102 |

| Table 59: | Port Control 12 (100M ports), Offset: 0x1000104                                 |

| Table 60: | Port Control 13 (100M ports), Offset: 0x1004                                    |

| Table 61: | EASE Register, Offset: 0x410-0x41C, 0x810-0x81C,0xC10-0xC1C,0x1008-0x100C107    |

| Table 62: | Definitions Used in Counter Descriptions                                        |

| Table 63: | Port MIB Counters                                                               |

| Table 64: | Pinout Differences                                                              |

| Table 65: | GT-48212 Pinout Table (Sorted by Pin Number)114                                 |

| Table 66: | GT-48208 Pinout Table (Sorted by Pin Number)115                                 |

| Table 67: | GT-48207 Pinout Table (Sorted by Pin Number)117                                 |

| Table 68: | Absolute Maximum Ratings                                                        |

| Table 69: | Recommended Operating Conditions                                                |

| Table 70: | DC Electrical Characteristics Over Operating Range                              |

| Table 71: | 208 PQFP Thermal Data                                                           |

| Table 72: | CPU Interface Timings                                                           |

| Table 73: | Switch Engine Interface Timings                                                 |

| Table 74: | MII, LED and MDC/MDIO Timings123                                                |

| Table 75: | Serial Clock Timings                                                            |

| Table 76: | 208 PQFP Package Dimensions                                                     |

| Table 77: | Document History                                                                |

NOTE: This document applies to all the Galaxy GT-482xx devices. All of the information is relevant specifically for the GT-48212 device (12 Ethernet ports and two Fast Ethernet ports). However, all of the functional descriptions are also relevant for all GT-482xx devices. The specific deviations and differences between the devices are described in section "Differences Between the GT-48212, GT-48208 and GT-48207" on page 12.

# 1. **GENERAL DESCRIPTION**

The GT-482xx is a high-performance, low-cost, Switched Ethernet Controller for 10+10/100Base-X that provides packet switching functions between 12 or 8 10Mbps and two 10/100Mbps ports. Switch expansion is possible by using one of the 100BaseX ports working with a separate oscillator. Switch expansion can reach up to 60Mhz clock frequency to achieve up to 240Mbps full duplex bandwidth. The GT-482xx can be used in both managed and unmanaged configurations.

The basic operation of the GT-482xx is quite simple. The GT-482xx receives incoming packets from the Ethernet or Fast Ethernet wire, searches in the Address Table for the Destination MAC Address and then forwards the packet to the appropriate port. If the Destination Address is not found, the GT-482xx treats the packet as a Multicast packet. The GT-482xx optionally forwards the packets to specified ports (or all ports in the VLAN, if enabled) and optionally to the CPU.

The GT-482xx automatically learns the port number of attached network devices by examining the Source MAC Address of all incoming packets. If the Source Address is not found in the GT-482xx Address Table, the device adds it to the table indicating on which port the address resides. The GT-482xx then notifies the CPU of the new address via a New\_Address message and an interrupt.

## 1.1 Fast Ethernet Ports

The GT-482xx integrates two Fast Ethernet ports. Each port works at 10/100Mbps (half duplex) or 20/200Mbps (full duplex). Two Media Independent Interfaces (MII) are provided for glueless connection to off-the-shelf PHY chips. Full Auto-Negotiation for both managed and unmanaged switches is supported.

One of the Fast Ethernet ports can be used for switch expansion. In this mode, it can operate at 60Mhz clock frequency to achieve up to 480Mbps full-duplex bandwidth. No special messages other than the regular Ethernet packets are passed between two Galaxy devices when connected with an expansion port. Management CPU treats two devices as separate devices which cannot share learning information. However, the CPU can control the learning (Section 6.4.1 "Port-Based VLAN Support" on page 28), and VLANs can be created by the CPU across the two devices so that the same VLAN can share ports on different devices.

The GT-482xx incorporates full MII management support. The MDC/MDIO pins are directly controlled by the CPU (and the Auto-Negotiation state machine, when enabled.)

## 1.2 Ethernet Ports

The GT-482xx integrates 12 or 8 10Mbps Ethernet ports. Each port works at 10Mbps (half duplex) or 20Mbps (full duplex) and includes the Media Access Control (MAC), Manchester encoder/decoder, link integrity logic, and a LED interface.

The GT-482xx Ethernet ports are compliant with both the 802.3 and Ethernet specifications. Each port contains three pins allowing direct interface with the AMD QuIET (see URL: www.amd.com) or the Tamarack TC3001 (see URL: www.tmi.com.tw) digital filters. Link indication from the PHY is serially shifted into the GT-482xx on the Link-Status pins.

Port #0 includes five pins (TxEn and Link Status are added) allowing interface to AUI, coax, or fiber-optic media.

#### 1.3 Flow Control and Back Pressure

IEEE standard 802.3x flow control (for full duplex) and proprietary back pressure (for half duplex) are supported on both the 100Mbps and 10Mbps ports. Back pressure or flow control is activated when the port or device buffer budget is almost exhausted.

#### 1.4 CPU Interface

The GT-482xx provides a simple interface for low-cost 32-bit bus processors operating at a 16-50Mhz clock rate. The GT-482xx provides glueless interface to the following processors:

- IDT 3041

- MIPS 64-bit CPUs (via the Galileo GT-64010A, GT-64011/14 and GT-64120 components)

- Motorola ColdFire CPUs (small amount of glue logic required for demuxed bus versions)

- Intel i960<sup>®</sup>Jx and i960<sup>®</sup>Rx

- Other CPUs may be attached to the GT-482xx via a PCI bus through the GT-64111 PCI Bridge/Bridge Memory Controller available from Galileo

In addition, the GT-482xx provides interface to the following processors requiring a minimum amount of glue logic:

- 80486 and derivatives

- i960<sup>®</sup>Cx and i960<sup>®</sup>Hx processors

- PowerPC 401/403 family

The CPU performs management functions such as:

- SNMP and RMON

- VLAN programming

- IP Multicast session initiation

- Spanning tree BDPU processing

- Packet trapping/transmission/reception

- Address table access and query.

- Layer 3 routing

**NOTE:** A CPU is not required in unmanaged GT-482xx configurations.

#### 1.5 Synchronous GRAM/DRAM Interface

The GT-482xx interfaces directly to 1 or 4 Mbytes of synchronous graphics RAM (SGRAM) or standard SDRAM. The DRAM is used to store the incoming/outgoing packets as well as the Address Table and other device data structures. The interface to the SGRAM is glueless; all signals needed to control the memory are provided.

The GT-482xx's SGRAM configurations are:

- 1 MByte (one 256K x 32 device): Address table contains up to 2K addresses, 512 Rx buffers.

- 4 Mbyte (two 1Mb x 16 device): Address table contains up to 8K addresses, 2048 Rx buffers.

#### 1.6 Address Recognition

The GT-482xx can recognize up to 8192 (2,024 in 1Mbyte configuration) different Unicast MAC addresses and unlimited Multicast/Broadcast MAC addresses. An intelligent address recognition mechanism enables filtering and forwarding packets at full Fast Ethernet wire speed. Hardware address aging and static address support is also included.

The GT-482xx provides an address self-learning mechanism. Each device has a private AddressTable located in its DRAM array. As the GT-482xx learns new addresses, it updates the CPU (if present) by sending a New\_Address message.

The GT-482xx performs Unicast address aging on its Address Table. This can be done automatically or when triggered by a CPU request. See Section 6.7 "Address Aging" on page 30

#### 1.7 IP Multicast and VLAN Support

When a management CPU is present, the GT-482xx traps IGMP packets over Ethernet/802.3 (on IPv4 and partial IPv6) and passes these to the CPU. The CPU may then program the port-mask (added to each entry in the Address Table) and the GT-482xx will lookup the Multicast and the Broadcast entries in the table and forward them according to the port-mask.

In addition, the CPU can program the port masks for Source Addresses. The GT-482xx forwards the Multicast and Broadcast packets according to the Source Address port masks only if the Multicast address is not present in the Address Table.

For Unicast packets, the GT-482xx checks that the source port appeared in the destination address port-mask bit and forwards the packet only if this bit is set. See also Section 6.4 "Locked Port" on page 27.

When unmanaged, the GT-482xx treats Multicast packets as Broadcast, and passes them to all ports, except for the source port.

#### 1.8 **Priority Queueing**

Each port, including the CPU has two transmit queues for high and low priority. The GT-482xx inserts the packet to the high priority queue if one of the following conditions occur:

- Priority bit in the Source Port Control register is set

- Priority bit in the Address Table is set for the destination address

- Priority bit in the Address Table is set for the source address

- The incoming packet contains a 802.1Q tag and the most significant bit of the Quality of Service field in the tag is set.

The CPU is able to force the priority regardless of the result of the above conditions. This is done by setting the ForcePri bit in the Port Control register. When ForcePri is set, the priority is defined only by the priority bit in the Source Port Control register.

In addition to the above conditions, all IGMP, BPDU, EASE sampled packets and New\_Address messages are entered into the CPU high-priority queue. All Unknown (both Unicast and Multicast) and Broadcast packets are entered into the low-priority CPU queue.

#### 1.9 Network Management Features

The GT-482xx provides comprehensive management capabilities enabling the switch OEM to implement a wide range of network management features.

For OEMs offering RMON capability, the GT-482xx provides per-port statistic counters to implement the first four groups of RMON.

The GT-482xx includes a unique packet sampling capability invented by the Hewlett-Packard Company called HP-EASE (Embedded Advanced Sampling Environment.) Each port has the ability to take "snapshots" of packet data at programmable intervals. These samples are forwarded to the management CPU for processing. The samples can be used to implement HP-EASE compatible messages for OpenView environments, or to create custom management information bases such as statistical RMON. Since packets are sampled using this technology, less local processing is required over standard RMON implementations. The source addresses of packet errors are also sent to the CPU allowing the switch OEM to support error counters in RMON host and matrix groups.

The GT-482xx includes hardware assistance for bridge-spanning tree algorithm and full hardware support for address aging.

# 1.10 Differences Between the GT-48212, GT-48208 and GT-48207

The differences between the three Galaxy devices are summarized in Table 1.

| Galaxy<br>Device | Functions not<br>implemented                                    | Pins Deleted                                                             | Note                                                                                                                             |

|------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| GT-48212         | N/A                                                             | N/A                                                                      | Baseline pinout                                                                                                                  |

| GT-48208         | Ethernet ports 1, 5, 7<br>and 11                                | All pins related to these ports                                          | To use a GT-48212 in a GT-48208<br>socket, the four unused Ethernet<br>ports must be properly disabled.                          |

| GT-48207         | Ethernet ports 1, 5, 7<br>and 11<br>Management CPU<br>interface | All pins related to the<br>these Ethernet ports and<br>the CPU interface | To use a GT-48212 in a GT-48207<br>socket, the four unused Ethernet<br>ports and the CPU interface must be<br>properly disabled. |

I

# 2. PINOUT

I

# 2.1 Pin Functions and Assignment

#### Table 2: Pin Functions

| Symbol              | Туре | Description                                                                                                                                                                                                                                                                                                                                                              |

|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU Interface       |      |                                                                                                                                                                                                                                                                                                                                                                          |

| Rst*                | I    | <b>RESET</b> : Active Low. Resets the GT-482xx to its initial state. This signal must be asserted for at least 10 MII clock cycles. Upon reset deassertion, the GT-482xx clears the internal empty list and the Address Table.                                                                                                                                           |

| ACIk                | I    | <b>Internal Clock:</b> This clock provides the timing for the GT-482xx internal units. All units, except for the Serial interface and the CPU interface, use this clock. This clock can vary between CClk and 66Mhz. AClk is also used to clock the synchronous DRAM. AClk frequency must be no higher than 4x CClk frequency.                                           |

| CCIk                | I    | <b>CPU Clock:</b> This clock provides the timing for the GT-482xx CPU interface.<br>The clock can vary between 16Mhz to 50Mhz. In unmanaged switch opera-<br>tion, CClk should be tied to the 25MHz 100Mbit PHY clock. CClk frequency<br>must not be lower than 25% of AClk frequency, and not higher than total<br>AClk frequency.                                      |

| AD[31:0]            | I/O  | <b>Address Data:</b> 32-bit multiplexed CPU address and data lines. During the first clock of the transaction, AD<31:2> contains a physical word address (30 bits). During subsequent clock cycles, AD<31:0> contains data.                                                                                                                                              |

| Blast*              | Ι    | <b>LAST in Burst:</b> Indicates the last word in the burst. The maximum burst size is 8 words. Blast* has alternate meanings depending on CPU mode.                                                                                                                                                                                                                      |

| Ready*              | 0    | <b>READY:</b> Indicates that AD[31:0] lines contain valid data. Ready* has alter-<br>nate meanings depending on CPU mode. This output pin features an open-<br>collector driver and should be tied as "wired-OR" in multiple GT-482xx<br>designs.                                                                                                                        |

| Ads*                | I    | Address Strobe: Indicates that AD[31:0] holds addresses (when deas-<br>serted it holds data). Ads* has alternate meanings depending on CPU mode.                                                                                                                                                                                                                         |

| W/R*                | I    | Write Read: Indicates Write/Read transaction. The polarity of this pin is pro-<br>grammable depending on CPU mode.                                                                                                                                                                                                                                                       |

| Int*                | 0    | <b>Interrupt:</b> Interrupt request line. Int* is asserted by the GT-482xx when one (or more) of the unmasked bits in the Interrupt Cause registers are set.                                                                                                                                                                                                             |

| BurstAddr[2:1]      | Ι    | <b>BurstAddr:</b> In 3041 mode, contains bits [3:2] of the physical-byte address.<br>In 64010/11 mode, contains bits [2:1] of the address. (See Table 16, "RESET<br>Pin Strapping Options," on page 66.)                                                                                                                                                                 |

| RdCen*/BurstAddr[0] | I/O  | <b>RdCen*/BurstAddr:</b> Read Buffer Clock Enable / Burst Address - In 3041 mode, this output pin indicates to the 3041 that the GT-482xx placed valid data on the AD bus. In 64010/11 mode, contains bit [0] of the address. When programmed to be an output, this pin features an open-collector driver and should be tied as "wired-OR" in multiple GT-482xx designs. |

| Symbol                                                                                                                                                                                                                                                                                                 | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                            |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DQM                                                                                                                                                                                                                                                                                                    | I/O  | <b>Data output mask:</b> In normal operation, used in read and write cycles to DRAM. During reset, this pin is sampled by the GT-48212 to indicate the DRAM size.The GT-482xx always accesses 32-bit values and does not require a separate DQM for each byte.<br>(See Table 16, "RESET Pin Strapping Options," on page 66.)                                                                           |  |

| DAddr[11:0]                                                                                                                                                                                                                                                                                            | I/O  | <b>DRAM Address:</b> In normal operation, Addr lines contains the DRAM address and bank selection. During reset, pins <11:0> are sampled by the GT-48212. (See Table 16, "RESET Pin Strapping Options," on page 66.)                                                                                                                                                                                   |  |

| Ras*                                                                                                                                                                                                                                                                                                   | I/O  | <b>Row Address Strobe:</b> In normal operation, indicates the Row Address.<br>During reset, this pin in conjunction with Cas* and WE* indicate the CPU<br>Type. (See Table 19, "CPU Mode Selection," on page 70.)                                                                                                                                                                                      |  |

| Cas*                                                                                                                                                                                                                                                                                                   | I/O  | <b>Column Address Strobe:</b> In normal operation indicates the Column<br>Address. During reset, this pin in conjunction with Ras* and WE* indicates<br>the CPU Type. (See Table 19, "CPU Mode Selection," on page 70.)                                                                                                                                                                                |  |

| CS*                                                                                                                                                                                                                                                                                                    | 0    | Chip Select: DRAM Chip Select. Indicates the DRAM chip select.                                                                                                                                                                                                                                                                                                                                         |  |

| WE*                                                                                                                                                                                                                                                                                                    | I/O  | Write Enable: In normal operation indicates DRAM write transaction.<br>During reset, this pin in conjunction with Ras* and Cas* indicates the CPU<br>Type.<br>(See Table 19, "CPU Mode Selection," on page 70.)                                                                                                                                                                                        |  |

| DData[31:0]<br>also used for configu-<br>ration parameters                                                                                                                                                                                                                                             | I/O  | D DRAM Data/GT-482xx parameters: Multiplexed 32-bit SGRAM data bus<br>and the GT-482xx parameters. In normal operation DData[31:0] connect<br>directly to the data input/output pins of the SGDRAM devices. During resist<br>some of these pins are sampled by the GT-482xx.<br>(See Table 16, "RESET Pin Strapping Options," on page 66).                                                             |  |

| 10Mbps Interface                                                                                                                                                                                                                                                                                       |      |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Transmit Data for the 10Mbps ports. During reset, these pins are sample<br>the GT-482xx to indicate the duplex mode. (See Table 16, "RESET Pin                                                                                                                                                         |      | <b>Transmit Data (Ethernet) / Duplex Mode</b> . In normal operation carries the Transmit Data for the 10Mbps ports. During reset, these pins are sampled by the GT-482xx to indicate the duplex mode. (See Table 16, "RESET Pin Strapping Options," on page 66).                                                                                                                                       |  |

| RxDE[11:0]         I         Receive Data (Ethernet): This pin carries the receive data for the 10N ports                                                                                                                                                                                              |      | Receive Data (Ethernet): This pin carries the receive data for the 10Mbps ports                                                                                                                                                                                                                                                                                                                        |  |

| In 10Base-T or 10Base-FL these pins are used as general purpose pins<br>They are sampled or driven according to the General Purpose register v<br>ues.<br>These pins are GP input pins by default, therefore, in 10BaseT and 10Ba<br>modes, these pins should be pulled HIGH or LOW through a 4.7K Ohm |      | Collision (Ethernet)/General Purpose pins: Collision detect in AUI mode.<br>In 10Base-T or 10Base-FL these pins are used as general purpose pins.<br>They are sampled or driven according to the General Purpose register val-<br>ues.<br>These pins are GP input pins by default, therefore, in 10BaseT and 10BaseF<br>modes, these pins should be pulled HIGH or LOW through a 4.7K Ohm<br>resistor. |  |

| TxEn[0]                                                                                                                                                                                                                                                                                                | IO   | <b>Transmit Enable:</b> In normal operation indicates that the packet is being transmitted on port 0.<br>During reset, this pin is sampled by the GT-482xx to indicate AUI type. (See Table 16, "RESET Pin Strapping Options," on page 66.)                                                                                                                                                            |  |

| Sclk                                                                                                                                                                                                                                                                                                   | I    | Serial Clock: 80Mhz clock. This clock is used to recover the receive data and to generate the transmit clock for the 10Mbps ports.                                                                                                                                                                                                                                                                     |  |

Table 2:

Pin Functions (Continued)

| Table 2: | Pin Functions | (Continued) |

|----------|---------------|-------------|

|----------|---------------|-------------|

| Symbol                                                                                    | Туре     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SerLinkStatus                                                                             | 1        | Serial Link Status Indication: This pin is used to serially shift the Link Sta-<br>tus of ports 1 to 11 from the external PHY. LEDClk and LEDStb are used to<br>clock and strobe the data (assertion of LedStb indicates the beginning of the<br>link data stream). SerLinkStatus pin is sampled at the rising edge of LedClk.<br>It should be driven at the falling edge of the LEDClk.<br>Polarity:<br>High SerLinkStatus: link is good<br>Low SerLinkStatus: link fail.<br>(See Figure 9: Example of Serial Link Status Indicator of Port 1 Link Fail on<br>page 47). |  |

| LinkStatus[0]                                                                             | 1        | Link Status Indication: This pin is used to indicate the Link Status of port 0<br>from the external PHY.<br>Polarity:<br>High LinkStatus[0]: link is good<br>Low LinkStatus[0]: link fail.<br>(See Figure 9: Example of Serial Link Status Indicator of Port 1 Link Fail on<br>page 47).                                                                                                                                                                                                                                                                                 |  |

| 10/100Mbps Interfac                                                                       | ce (MII) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| TxEn[1:0]                                                                                 | 0        | <b>Transmit Enable:</b> Active HIGH. This output indicates that the packet is being transmitted. TxEn is synchronous to TxClk.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| TxClk[1:0]                                                                                | I        | <b>Transmit Clock:</b> Provides the timing reference for the transfer of TxEn, T signals. TxClk frequency is one fourth of the data rate (25 MHz for 100Mbg 2.5 MHz for 10Mbps, 60Mhz for 240Mbps). TxClk nominal frequency show match the nominal frequency of RxClk for the same port.                                                                                                                                                                                                                                                                                 |  |

| TxD0[3:0]                                                                                 | 0        | Transmit Data 0: Outputs the Port0 Transmit Data. Synchronous to TxClk[0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| TxD1[3:0]                                                                                 | 0        | Transmit Data 1: Outputs the Port1 Transmit Data. Synchronous to TxClk[1].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Col[1:0]                                                                                  | I        | <b>Collision detect:</b> Active HIGH. Indicates a collision has been detected on the wire. This input is ignored in full-duplex mode. Col is not synchronous to any clock.                                                                                                                                                                                                                                                                                                                                                                                               |  |

| RxD0[3:0]                                                                                 | I        | Receive Data 0: Port 0 Receive Data. Synchronous to RxClk[0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| RxD1[3:0]         I         Receive Data 1: Port 1 Receive Data. Synchronous to RxClk[1]. |          | Receive Data 1: Port 1 Receive Data. Synchronous to RxClk[1].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| RxEr[1:0]                                                                                 | I        | <b>Receive Error</b> . Active HIGH. Indicates that an error was detected in the received frame. This input is ignored when RxDV for the same port is inactive.                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| RxClK[1:0]                                                                                | I        | <ul> <li>Receive Clock. Provides the timing reference for the transfer of the RxDV,RxD,RxEr signals (per port). Operates at either 25 MHz (100Mbps), 2.5 MHz (100Mbps) or 60Mhz (240Mbps). The nominal frequency of RxClk (per port) should match the nominal frequency of that port's TxClk.</li> </ul>                                                                                                                                                                                                                                                                 |  |

| RxDV[1:0]                                                                                 | I        | <b>Receive Data Valid:</b> Active HIGH. Indicates that valid data is present on the RxD lines. Synchronous to RxClk.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| CrS[1:0]                                                                                  | I        | <b>Carrier Sense:</b> Active HIGH. Indicates that either the transmit or receive medium is non-idle. CrS is not synchronous to any clock.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Symbol                      | Туре     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                       |  |  |  |  |  |

|-----------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MDC                         | 0        | <b>Management Data Clock:</b> Provides the timing reference for the transfer of the MDIO signal. This output may be connected to the PHY devices of both ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                       |  |  |  |  |  |

| MDIO                        | I/O      | Management Data Input/Output: This bidirectional line is used to transfer control information and status between the PHY and the GT-482xx. It conforms with IEEE Std 802.3. This signal may be connected to the PHY devices of both ports. When not driven by an MII compliant PHY, this pin must be connected to a pull-up or pull-down resistor. PHY register reads performed by the GT-482XX will be decoded as all 1's or all 0's respectively."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                       |  |  |  |  |  |

| LED Interface Pins          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                       |  |  |  |  |  |

| LEDStb/LEDMode              | I/O      | operation, envelo<br>bit#27) of a valid<br>LED mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>LED Strobe/LED Mode:</b> Multiplexed LED Strobe and LED mode. In normal operation, envelopes the full-duplex and Link-status data stream (bit #0 to bit#27) of a valid data frame on LEDData output. During reset, indicates the LED mode.<br>(See Table 16, "RESET Pin Strapping Options," on page 66.) |                                                                                                                                                                                                       |  |  |  |  |  |